Richtlinien für das Leiterplatten-Layout von LED-Treibern im Fahrzeug

Bei Leiterplatten-Layouts für Automotive-Anwendungen sind strikter Standards anzuwenden, was die elektromagnetische Verträglichkeit (EMV), die Betriebstemperaturen und die instationären Betriebszustände betrifft. Eine Applikationsschrift.

Anbieter zum Thema

Die vorliegende Applikationsschrift beschreibt einige grundlegende Gedanken zum Leiterplatten-Design für LED-Treiber mit Gleichspannungswandlern. Der Baustein LP8863-Q1 und das zugehörige EVM werden dabei als Beispiele herangezogen. Zur Sprache kommen allgemeine Regeln und Beispiele für besseres Leiterplatten-Design, die sich auch auf andere Bereiche anwenden lassen.

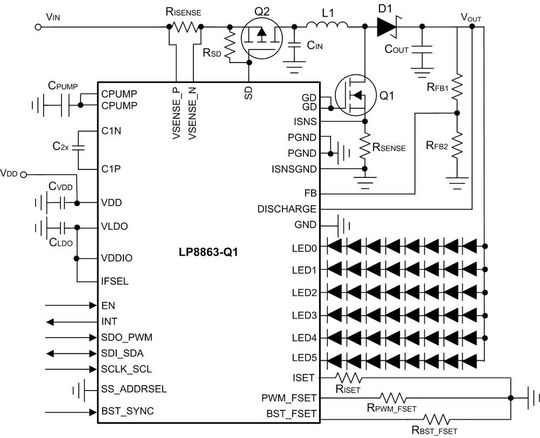

Typische Anwendungsschaltung

Bei dargestellten Anwendungsschaltung handelt es sich um eine gängige LED-Treiberschaltung mit einem Powerline-FET, Strommesswiderständen, einer Spule, Ein- und Ausgangskondensatoren für den Aufwärtswandler, einem Schalt-FET, einer Diode, Kondensatoren für die interne Ladungspumpe und einer Hostschnittstelle. Zusätzlich wurde das LP8863-Q1 EVM mit einem EMI-Filter bestückt, um Gleichtaktstörungen des Systems zu unterdrücken.

Entscheidende Faktoren

Die Richtlinien in diesem Artikel sind nach Wichtigkeit geordnet. Begonnen wird mit jenen, die in den meisten Anwendungsfällen die größten Auswirkungen haben.

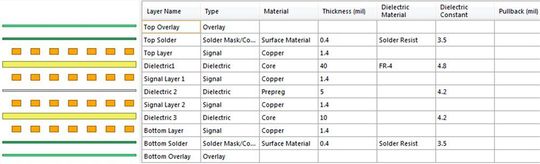

Leiterplattenlagen

Nach Möglichkeit wird empfohlen, eine mindestens vierlagige Leiterplatte zu verwenden, um rauschbehaftete Knoten von anderen Teilen des Systems zu isolieren und jeder Signal- und Stromversorgungsleitung einen möglichst kurzen Weg zur Masse zu bieten. Zu diesem Zweck sollte eine der Innenlagen als Massefläche dienen.

Ist die Leiterplatten nur zweilagig, ist unter Umständen keine effektive Rauschisolation möglich, und die Masseverbindung kann sich gegenüber einer vierlagigen Leiterplatte unnötig verlängern. Bei einem zweilagigen Design muss zwischen Kosten und Leistungsfähigkeit abgewogen werden.

Erste Lage (oben): Signale, Stromversorgung und Masse. Sämtliche Bereiche mit Ausnahme der Signale und Stromversorgungsleitungen sind mit Kupfer ausgefüllt, das zur Isolation der Leiterbahnen mit der Masse verbunden ist.

Zweite Lage (Signallage 1): Massefläche für die digitalen Signale und die Stromversorgung.

Dritte Lage: (Signallage 2): Signale, Stromversorgung und Masse. Sämtliche Bereiche mit Ausnahme der Signale und Stromversorgungsleitungen sind mit Kupfer ausgefüllt, das zur Isolation der Leiterbahnen mit der Masse verbunden ist.

Vierte Lage (unten): Signale, Stromversorgung und Masse. Sämtliche Bereiche mit Ausnahme der Signale und Stromversorgungsleitungen sind mit Kupfer ausgefüllt, das zur Isolation der Leiterbahnen mit der Masse verbunden ist.

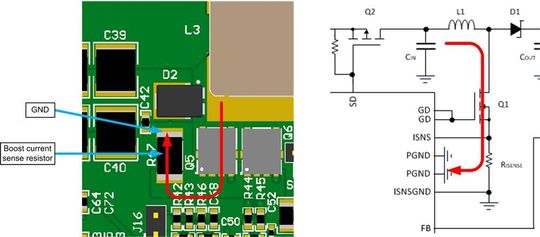

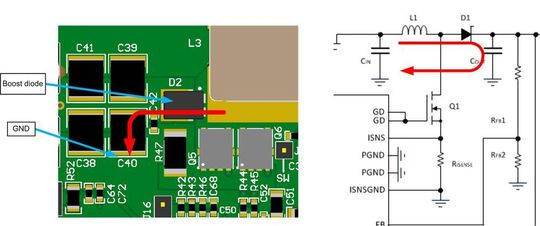

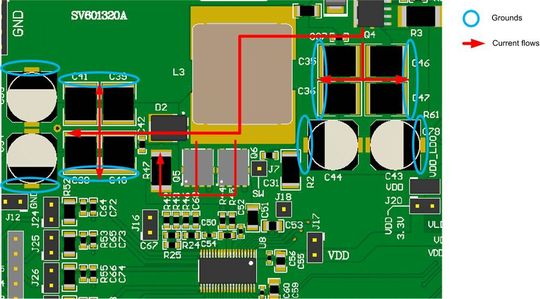

Stromschleifen

Im Aufwärtswandler kommen zwei Haupt-Stromschleifen vor. Diese erzeugen magnetische Felder, die auf andere Schaltungen im System einwirken können. Da die Stärke des Magnetfelds proportional zu der von der Schleife umschlossenen Fläche ist, sollte diese nach Möglichkeit minimiert werden. Die Bilder 3 und 4 zeigen die beiden Stromschleifen.

Die wichtigsten Stromwege und die Platzierung der Bauelemente sind aus Bild 5 zu entnehmen. Die Masse des Stromversorgungs-Eingangs, der Schalter und der Ausgang sind zentral angeordnet, und alle Bauteile sind mit ausreichend Durchkontaktierungen versehen, um einen möglichst kurzen Weg zur Masse bereitzustellen.

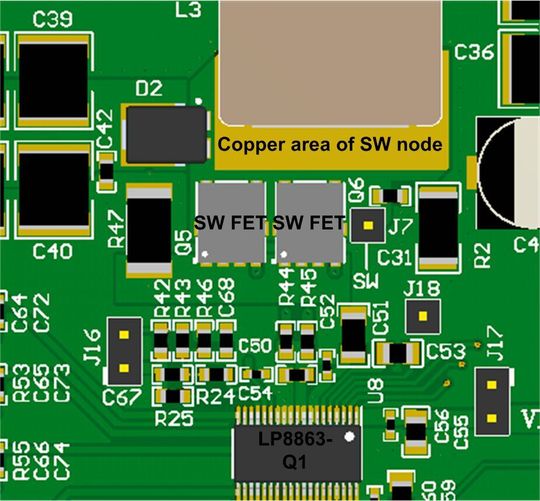

Der Schalt-FET

Im Schalt-FET entstehen Leitungs- und Schaltverluste. Erstere werden durch den Einschaltwiderstand des FET verursacht und sind proportional zum Strom. Minimieren lassen sie sich durch die Wahl eines FET mit genügend kleinem RDS(on). Die Schaltverluste sind dagegen proportional zum Spannungsausschlag, zur Frequenz und zur Anstiegs- und Abfallzeit. Sie können insbesondere bei hohen Schaltfrequenzen einen großen Anteil an den Gesamtverlusten ausmachen, zumal es aufgrund der begrenzten FET-Performance unter Umständen nicht möglich ist, einen genügend großen oder schnellen FET zu wählen.

Wegen der eingeschränkten Fähigkeiten des FET und der Eigenschaften des Gleichspannungswandlers kommt es unweigerlich zu einer Erwärmung des Schalt-FET, sodass beim Leiterplatten-Design entsprechende Vorkehrungen für eine gute Ableitung der Wärme zu treffen sind. Bild 6 zeigt den Schaltknoten. Es werden zwei Schalt-FETs eingesetzt, um die auf den einzelnen Baustein entfallenden Verluste zu verringern.

Das Vergrößern der Schaltknoten-Fläche muss mit Bedacht erfolgen, da sich verschiedene Nebeneffekte einstellen können.

1: Die größere Kupferfläche lässt die parasitäre Kapazität des Schaltknotens ansteigen. Die daraus resultierenden längeren Schaltzeiten führen wiederum zu höheren Schaltverlusten.

2: Eine große Kupferfläche kann wie eine Antenne wirken und sich auf die elektromagnetische Verträglichkeit auswirken.

Folglich müssen beim Vergrößern der Kupferfläche des Schaltknotens gewisse Abstriche gemacht werden. Bei hohen Schaltfrequenzen empfiehlt TI eine Fläche, die um einen geringen Faktor größer ist als der Footprint des FET. Bei niedrigen Schaltfrequenzen von beispielsweise wenigen hundert Kilohertz ist die Fläche des Schaltknotens nicht so entscheidend für die Schaltverluste und die Wärmeableitung.

Überlegungen zum Stromfluss

Der Schaltstrom fließt vom Schalt-FET zum Strommesswiderstand und über Durchkontaktierungen zur Massefläche. Dieser Stromweg muss ausreichend groß dimensioniert sein. Wie die Leiterbahnbreite zu berechnen ist, ist in Abschnitt 11 beschrieben. Die Zahl der Durchkontaktierungen lässt sich an Hand der Stromtragfähigkeit einer Durchkontaktierung ermitteln (siehe Gleichung 1).

Stromtragfähigkeit [in A] = k x TempAnstieg [in °C]b x Fläche [in mil²]c

Darin sind:

Fläche = π x (Innendurchmesser+Kupferdicke) x Kupferdicke

Für IPC-2221-Außenlagen gilt:

k = 0,048, b = 0,44, c = 0,725, Kupferdicke(min) = 1 mil

Auf dem LP8863-Q1 EVM dient eine Durchkontaktierung mit einem Durchmesser von 8 mil dazu, den Strommesswiderstand mit der Massefläche zu verbinden. Ein sinnvoller Schätzwert für die Stromtragfähigkeit dieser Durchkontaktierung lautet etwa 1,49 A bei einem Temperaturanstieg von 10 °C. Für die Masseverbindung des Strommesswiderstands wurden im vorliegenden Fall 12 Durchkontaktierungen verwendet, was einem Strom von bis zu 17,88 A entspricht – genug also für den maximalen Schaltstrom von ca. 10 A. Gleichung 1 kann auch für andere Stromwege mit hohen Stromstärken benutzt werden, die Durchkontaktierungen erfordern.

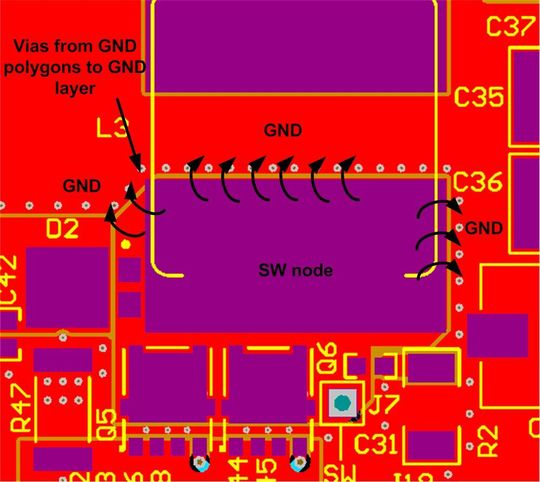

Isolation des rauschbehafteten Schaltknotens

Eine effektive Isolation des rauschbehafteten Knotens verbessert die EMV-Eigenschaften des ganzen Systems, denn der Schaltknoten des Gleichspannungswandler kann wie eine Antenne wirken und hochfrequente elektromagnetische Störgrößen emittieren. Wenn man diesen Knoten mit kurzen Masseverbindungen umgibt, lässt sich eine effektive Isolation der Störgrößen erzielen, indem die Kopplung in andere Schaltungen aufgehoben und die Störungen stattdessen durch die Bildung kleinerer Schleifen lokal begrenzt wird. Wie in Bild 7 zu sehen ist, ist der Schaltknoten von einem Polygon umgeben, das über Durchkontaktierungen auf kurzem Weg mit Masseflächen verbunden ist.

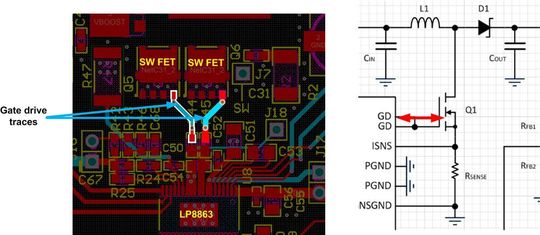

Leiterbahn des Gatetreibersignals

Die Leiterbahn, die das Gatetreibersignal des Schalt-FET überträgt, muss möglichst kurz und breit sein, um die Induktivität und den Widerstand gering zu halten, damit Oszillationen und eine Verlängerung der Anstiegs- und Abfallzeiten vermieden werden. Es handelt sich hier um eine der entscheidendsten Leiterbahnen eines Aufwärtswandlers.

Der LED-Treiber

Im LED-Treiber können Verluste durch die Spannungsdifferenz zum LED-String entstehen. Wenn sich die Gesamt-Vorwärtsspannungen (Vf) der einzelnen LED-Strings stark unterscheiden, entstehen an den LED-Treiber-Eingängen mit der größten Spannungsdifferenz (also am LED-String mit dem niedrigsten Vf-Wert) die geringsten Verluste. Damit es zu keiner übermäßigen Erwärmung des LED-Treibers kommt, muss sein Die-Attach Pad (DAP) über viele Durchkontaktierungen und/oder breite Leiterbahnen mit der Massefläche verbunden sein. Auf dem LP8863-Q1 EVM verbinden insgesamt zwölf Durchkontaktierungen mit einem Außendurchmesser von 20 mil das DAP des Bausteins mit der Massefläche.

Durchkontaktierungen am DAP helfen die Temperatur zu senken und ergeben außerdem einen ausreichend dimensionierten Stromweg für den LED-Treiber (das DAP ist gleichzeitig die LED-Masse). Der Wärmewiderstand jeder Durchkontaktierung beträgt geschätzt ca. 26 °C/W (siehe Gleichung 2). So lässt sich für die erwartete Verlustleistung des LED-Treibers und die Temperaturbedingungen die Zahl der benötigten Durchkontaktierungen errechnen.

θcu-via = L / (K × π x (DO² – DI²) / 4

Darin sind:

- L: Länge der Durchkontaktierung

- K: Wärmeleitfähigkeit von Kupfer (9 W/Zoll °C)

- DO: Außendurchmesser der Durchkontaktierung (20 mil)

- DI: Innendurchmesser der Durchkontaktierung (8 mil)

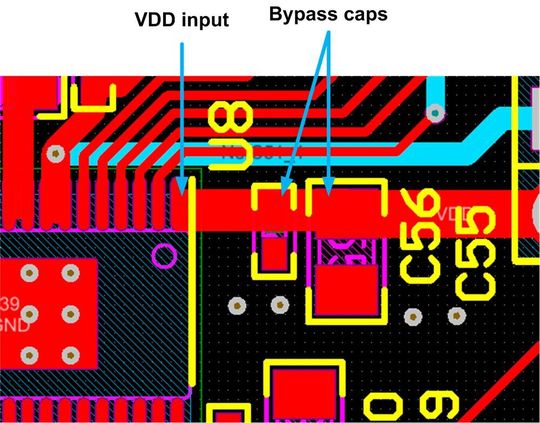

Logik-Stromversorgung

Die Logik-Stromversorgung des LED-Treibers kann Störgrößen oder Welligkeiten aufweisen, die die digitalen (oder sogar auch die analogen) Funktionen des Bausteins beeinträchtigen können. Diese Störgrößen und Welligkeiten müssen deshalb vor dem LED-Treiber herausgefiltert werden. Im Normalfall dient eine Kapazität von beispielsweise 0,1 µF als Tiefpassfilter. Die entsprechenden Kondensatoren sollten möglichst nah am Eingangs-Pin platziert werden.

Leiterbahn für das Rückkopplungssignal des Aufwärtswandlers

Das Rückkopplungssignal des Aufwärtswandlers wird vom LED-Treiber an den Regelkreis zurückgeführt. Diese Verbindung muss isoliert sein, damit sie nicht durch externe Störgrößen oder Übersprechen benachbarter Signale beeinträchtigt wird und die stabile Regelung des Aufwärtswandlers nicht gestört wird. Wie man in Bild 10 erkennen kann, ist die Leiterbahn des Rückkopplungssignals durch ein Masse-Polygon und Durchkontaktierungen zur Massefläche vom Schaltknoten des Aufwärtswandlers isoliert.

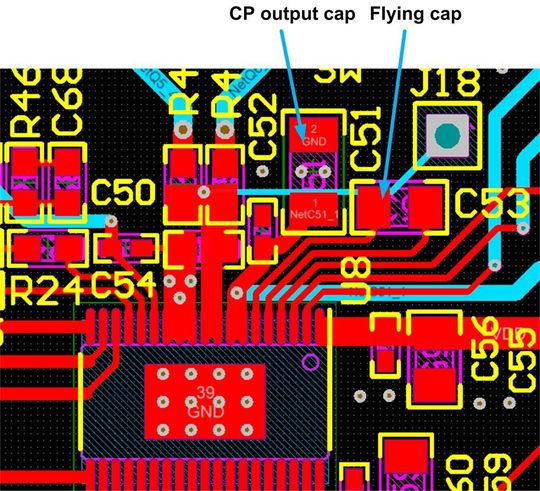

Ladungspumpe

Der LP8863-Q1 verfügt über eine eingebaute Ladungspumpe, um aus der von außen angelegten Versorgungsspannung die doppelt so hohe Gate-Treiberspannung zu erzeugen. Für die Ladungspumpe werden mindestens zwei Kondensatoren benötigt – ein „fliegender“ Kondensator für das Schalten der Ladungspumpe und ein Ausgangskondensator. Beide sollten möglichst nah am Ladungspumpen-Controller angeordnet sein, damit es nicht durch parasitäre Effekte zu Störungen und Oszillationen kommt. Die Breite der Leiterbahnen zum fliegenden Kondensator und zum Ausgangskondensator muss so gewählt werden, dass es beim maximalen Treiberstrom der Ladungspumpe zu keinem übermäßigen Spannungsabfall und zu keiner Wärmeentwicklung kommt.

Powerline-FET

Ein Powerline-FET in der Stromversorgungs-Leitung kann, muss aber nicht verwendet werden. Wird dieser FET weggelassen, muss die Leiterbahn so breit sein, dass der aufgenommene Strom zu keiner übermäßigen Erwärmung führt. Kommt dieser FET dagegen zum Einsatz, muss die Leiterbahn wesentlich breiter als der FET sein, da auch die Verlustwärme des FET abgeführt werden muss. Die Verlustleistung des Stromversorgungs-FET lässt sich einfach mit der Formel P = IIN² x RDS(on) berechnen. Die Sperrschichttemperatur beträgt RθJA × P + Umgebungstemperatur, wenn die Leiterplattenfläche wie im Datenblatt des FET angegeben ein Quadratzoll beträgt. Ist zu erwarten, dass die Chiptemperatur die maximal zulässige Sperrschichttemperatur des FET übersteigen wird, muss die Kupferfläche des Powerline-FET (auf der Seite des Wärmeableit-Pads bzw. des Drain-Anschlusses) vergrößert werden.

Stromversorgungs-Leiterbahn für den Aufwärtswandler

Die Stromversorgungs-Leiterbahn für den Aufwärtswandler muss so breit sein, dass die Temperatur innerhalb der vorgegebenen Grenzen bleibt. Die erforderliche Mindestbreite lässt sich mit Gleichung 3 berechnen:

Breite = (Strom [in A] / k x (Temp_Anst [in -°C])b))(1/c)) / Dicke [in mil]

Darin sind:

- Für IPC-2221-Innenlagen: k = 0,024, b = 0,44, c = 0,725

- Für IPC-2221-Außenlagen: k = 0,048, b = 0,44, c = 0,725

Der maximale Eingangsstrom des LP8863-Q1 beträgt 11,5 A, die Dicke der Leiterbahn 1,4 mil und die Breite ca. 260 mil. Folglich beträgt die zu erwartende Temperaturzunahme bei maximalem Eingangsstrom etwa 15 °C. Dieser Temperaturanstieg darf nicht größer sein als die erwartete Temperaturzunahme der einzelnen Bauelemente des Aufwärtswandlers. Auf dieselbe Weise lässt sich die Breite der Leiterbahn zwischen Schalt-FET und Masse (über den Strommesswiderstand) berechnen.

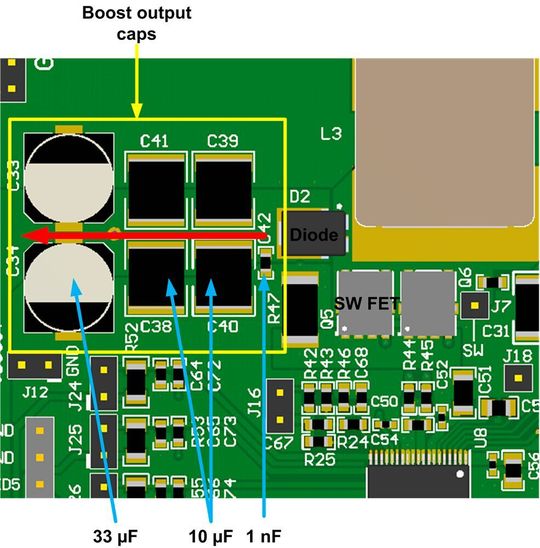

Platzierung der Kondensatoren

Störgrößen aus dem Schaltknoten pflanzen sich über die Diode und die Ausgangs-Leiterbahnen fort, während hochfrequente Störgrößen bei kurzen Antennenlängen leicht elektromagnetische Interferenzen erzeugen können. Diese hochfrequenten Störungen entstehen durch Oszillationen und Übergangszustände beim Schalten und können Frequenzen vom dreistelligen Megahertz-Bereich bis zu einigen Gigahertz erreichen. Ausgangs-Leiterbahnen von wenigen Zoll ergeben gute Antennen für Frequenzen in dieser Größenordnung. Deshalb ist das Ausfiltern dieses Frequenzbereichs eine besonders effektive Maßnahme zur EMI-Reduzierung. Zu diesem Zweck wird empfohlen, die größeren Kondensatoren am Schaltknoten durch Kondensatoren mit kleineren Kapazitätswerten zu ergänzen, wie es in Bild 12 dargestellt ist.

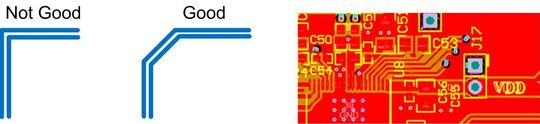

Leiterbahnen für die digitalen Steuersignale

Meist ist für die digitalen Steuersignale von LED-Treibern kein besonderes Routing erforderlich, da die Frequenzen dieser Signale in der Regel eher gering sind und maximal im zweistelligen Megahertz-Bereich liegen. Allerdings können plötzliche Impedanzänderungen durch spitze Winkel oder Dickenänderungen an bestimmten Stellen der Leiterbahn wie Antennen für hochfrequente Anteile (z. B. Oszillationen oder Welligkeiten) wirken. Bild 13 veranschaulicht, wie die Leiterbahnen verlegt werden sollten.

Zusammenfassung

Wegen der hohen Schaltfrequenzen und der hohen Ströme bekommt das Leiterplatten-Design für LED-Treiber hoher Leistung einen immer höheren Stellenwert. Die Restriktionen, die sich aus den verwendeten Bauelementen oder der Applikation selbst ergeben, lassen es möglicherweise nicht zu, alle Anforderungen zu erfüllen. Ein sorgfältig ausgearbeitetes Leiterplatten-Layout aber kann das Spektrum der in Frage kommenden Anwendungen erweitern und verbessert außerdem die Stabilität des Systems. Neben den allgemeinen Empfehlungen, die in diesem Beitrag gegeben wurden (z. B. Verkleinern von Stromschleifen, Verwendung möglichst breiter Leiterbahnen, Bereitstellung genügend großer Wärmeableitflächen) trägt auch das Isolieren störungsbehafteter Knoten und die korrekte Platzierung der Bauelemente zur Verbesserung des Leiterplattendesigns und zu einer einfacheren Systementwicklung bei.

* Sungho Yoon it als Applications Engineer für Texas Instruments tätig.

(ID:46584576)

:quality(80)/p7i.vogel.de/wcms/36/b6/36b6ec7d0f62f63c3afed29ac7ee35e1/0130761304v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bb/95/bb95bde7af92f5e6ea1c3907ee0339a1/0130757742v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ed/e5/ede508b1f610d78805cac43fa14d2d8d/0130745704v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/91/96/9196281a2b2f77472433d99b94d7638b/0130743410v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/5d/22/5d22f301eec5be6dc3e06232ca757a54/0130870631v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/5b/02/5b0226319b3ee00eb76435c9686c0d84/0130860779v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f7/62/f762cd668bb9943b59b7b411e0fd725a/0130825465v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/80/ab/80ab8285a83d0df1c48c73e9e7106f81/0130822084v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/db/aa/dbaadddb058a27b7672c293ec99dc177/lufthansa-20city-201920-kux-7195-1800x1012v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/4d/5c/4d5cb18f947990b0c047b0621e1d0d4b/0130820491v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/65/bc/65bc7577403c20468ea39fa0fad6686c/0130696698v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/7a/0d7a064833b2063be11e2b2aa4ec8fbb/0130697677v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c3/68/c368a3ad72ac970809451c311e05a07b/0127817359v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6a/4f/6a4f63cfca5e01026d25edd19b5302c5/0127761368v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/42/86/4286fd057b5413102fbac1758d2dc55f/0127713923v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/36/49/36496a26b0c295de6d9a36d66ea7571a/0125402418v3.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/62/16/621651a93b1ef/logo-we-rgb-pos.png)

:quality(80)/p7i.vogel.de/wcms/5c/e4/5ce41ec6c6dc30a9f017266e71d9ade6/0125425439v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/bc/24/bc2428d8e9ac80186649403076b3193f/0125220776v2.jpeg)